# PHLOGON: PHase-based LOGic using Oscillatory Nano-systems

Tianshi Wang and Jaijeet Roychowdhury

Department of EECS, The University of California, Berkeley, CA, USA {tianshi,jr}@berkeley.edu

Abstract. In this paper we take a fresh look at Goto and von Neumann's phase-based logic ideas, provide enhancements that can overcome major limitations of their previous implementations. We show that with injection locking serving as the central mechanism, almost any DC-powered, self-sustaining nonlinear oscillator — including electronic, spintronic, biological, optical and mechanical ones — can be used to build fundamental components — including latches and combinatorial elements in a phase logic based computing architecture. We also discuss noise immunity and potential power dissipation advantages that can be achieved under this scheme.

Keywords: Phase-based logic, nonlinear oscillators, injection locking.

#### 1 Introduction

In the 1950s, Eiichi Goto and John von Neumann invented a new paradigm for computing: *temporal encoding* of logical states using phases of oscillatory signals [39,36,41,9]. Phase logic schemes corresponding to it have been implemented physically [13,28,27,35,25], indeed were popular in Japan in the 1950s due to their simplicity and reliability. However, the advent of transistors and integrated circuits led to their demise, since the devices and circuits they were based on could not compete with level-based logic using transistors.

A key reason for their lack of competitiveness was size and miniaturizability. Specifically, they normally require inductors and large capacitors, which are bulky compared to semiconductor transistors, particularly today's nano-scale MOS devices. Another related reason was *lower operating speed*, stemming not only from larger component sizes, but also from inherent features of von Neumann's scheme (*e.g.*, periodic turn-on transients and delays in logic gates) that made phase-based logic slower than transistorized level-based logic. Later attempts (from the 1980s to the present) used superconducting Josephson-junction devices [15], which are fast, but still limited in terms of miniaturizability and practical deployment at room temperature. Therefore, these implementations were quickly overshadowed by the rise of transistorized level-based logic, which has dominated logical computing for decades.

With power dissipation, variability and noise having emerged as serious barriers to semiconductor scaling and Moore's law — both synonymous with progress

DOI: 10.1007/978-3-319-08123-6\_29, © Springer International Publishing Switzerland 2014

in computing — there has been renewed interest in Goto and von Neumann's phase-based logic ideas. Recently MEMS-based replacement for von Neumann's circuit has been proposed [21]. It could perform bit storage and bit flip operations under AC power and its success in implementing computation and large-scale integration is yet to be seen. In this paper, we propose enhancements (collectively termed **PHLOGON**) to Goto and von Neumann's schemes that employ self-sustaining oscillators as basic phase logic elements to eliminate the size and integrability limitations of the previous implementations, opening possibilities for robust, general-purpose computing substrates that offer significant noise immunity and potential power dissipation advantages over level-based CMOS computing.

We describe how the core computational block — a finite-state machine (FSM) can be built using phase-based logic. As an example, we show how it can be realized using *CMOS ring oscillators in standard existing technologies*. However, PHLOGON is not limited to electronic oscillators. Indeed, it can use almost any self-sustaining nonlinear oscillator — including spintronic, biological, optical and mechanical ones – as the underlying logical element, expanding the implementation scope of Goto and von Neumann's phase logic ideas greatly.

To better explain our ideas, we provide background on Goto and von Neumann's phase-based computing scheme by summarizing von Neumann's related works in Sec. 2. In Sec. 3.1 we illustrate how sub-harmonic injection locking leads to multiple stable phase states, serving as the key mechanism for encoding phase logic. We show that phase logic offers inherently greater immunity to noise, interference and variability (Sec. 3.2). We then describe our implementation of phase-based computing architecture using self-sustaining nonlinear oscillators (Sec. 3.3) and discuss its potentially lower power/energy operation compared with traditional level-based CMOS computing scheme (Sec. 3.4). Conclusions are provided in Sec. 4.

### 2 John von Neumann's Phase Logic Scheme

In his patent [39,36,41], von Neumann outlined fundamental ideas and a complete scheme for phase-based computing. We provide a brief sketch of the main ideas here.

von Neumann started with a key observation: the circuit in Fig. 1(a) can feature two (or more) distinct oscillating steady states, which can be used to store two (or more) logical states stably. The circuit features a lossless, nonlinear, charge-controlled capacitor (shown towards the left of Fig. 1(a)), together with bandpass filters used to isolate an AC power source or pump  $(V_g)$ , and an output load  $(R_L)$ , from the several frequencies simultaneously present in the capacitor's terminal voltage. When the amplitude of the AC pump voltage waveform, assumed sinusoidal at frequency  $f_0$ , is larger than a critical threshold  $V_c$ (Fig. 1(b)), the voltage waveform across the capacitor can feature components that are integer sub-multiples of  $f_0$ , i.e., sub-harmonics of  $f_0$ . Furthermore, as depicted in Fig. 1(c), a generated sub-harmonic can be in one of several distinct

(a) AC-powered subharmonic gener- (b) Multistability beyond (c) Example: discriminating beator features multiple phase-shifted a critical pump amplitude, tween subharmonic steady states stable states [41, Fig. 2].  $V_c$  [41, Fig. 4]. [41, Fig. 6].

Fig. 1. von Neumann's basic phase-based latch: a nonlinear AC-pumped circuit with multiple subharmonic steady states

phase relationships with respect to the waveform of the AC pump. Each distinct phase relationship can be used to encode a logic state. The circuit functions, effectively, as a *latch* that can store a logic value. The sub-harmonic and multi-stability properties of the circuit in Fig. 1(a) can be inferred from an elegant formula, the *Manley-Rowe relationships* [39,23,41].

(a) Amplitude modulation of (b) A ring of latches can retain (c) Phase-shifted amplitude the AC pump to capture an in- a phase-logic state permanently modulation waveforms driving put logic value [41, Fig. 7].

[41, Fig. 11]. the ring of latches [41, Fig. 11].

Fig. 2. von Neumann's scheme for setting a latch to an input state and retaining it

Setting a phase-encoded latch to an input logic state: Having devised a latch circuit capable of storing logical values encoded in phase, von Neumann considered the question of setting a latch to a desired logic state supplied as input. He proposed a scheme based on modulating the amplitude of the AC pump slowly with a waveform similar to the uppermost graph of Fig. 2(a). When this modulation waveform is low, the latch is, effectively, turned off; as the modulation increases and magnitude of the AC pump crosses the critical threshold  $V_c$ , the latch turns on and settles to one of the possible logic states. von Neumann suggested that if a desired logic value (encoded in phase) were to be introduced as an input to the latch just as it was turning on, the latch would settle to (the sub-harmonic phase corresponding to) the same logic value. This is depicted in the middle and bottom graphs of Fig. 2(a).

<u>Holding on to the logic state</u>: A problem with the above input-latching scheme is, of course, that the latch is turned off periodically, thereby losing its stored state. von Neumann's solution was a ring of latches (Fig. 2(b)), with each latch's AC pump modulated by a phase shifted version of its predecessor's AC modulation (Fig. 2(c)). The ring operates in merry-go-round fashion, with each succeeding latch turning on, capturing its predecessor's logic state and retaining it as the predecessor subsequently turns off. At any given time, one latch is always on, hence the logic state is never lost.

<u>Combinatorial operations for phase-encoded logic</u>: Next, von Neumann turned to the problem of realizing arbitrary Boolean operations using phase-encoded logic. Noting that two operations, NOT and MAJORITY, constitute a logically complete set <sup>1</sup>, he provided especially elegant means of realizing them [41]. NOT is obtained simply by a through connection between latches with different pump modulation phases while MAJORITY is obtained simply by adding the waveforms of the three inputs together.

Having devised phase-based realizations of the latch-ring and the logically complete combinatorial function set NOT and MAJORITY, together with a consistent timing scheme provided by the phase shifted pump modulation waveforms, von Neumann had developed all the basic components needed to make state machines and general computing architectures.

# 3 PHLOGON: Key Concepts

As discussed before in Sec. 1, previous implementations of von Neumann's scheme suffer from limitations and have not, to date, been miniaturisable or large-scale integrable. In this section, we detail our ideas for PHLOGON, explain their novelty and significance.

#### 3.1 Sub-harmonic Injection Locking (SHIL) Enables Phase Logic

A central paradigm in PHLOGON is that DC-powered nonlinear self-sustaining oscillators can be used as phase logic elements. This paradigm relies on the fact that such oscillators inherently feature a property known as *injection locking* [16,2,19], which enables the oscillator's waveforms to move in lock-step with – *i.e.*, become *phase locked* to – a small external signal injected into it<sup>2</sup>. Injection locking is responsible for many *sychronization phenomena* in nature (*e.g.*, the synchronized flashing of fireflies [4,34,33]) and is exploited in engineering (*e.g.*, injection locked frequency dividers [30]).

A specific type of injection locking, known as sub-harmonic injection locking (SHIL), is the key mechanism involved in phase logic encoding. We have developed theory that shows how SHIL leads to multiple stable phase states[1], as depicted in Fig. 3(b). We have also been able to distill the essential properties needed in an oscillator for it to be an effective sub-harmonically locked oscillator-latch. We provide a sketch of our ideas and results here.

<sup>&</sup>lt;sup>1</sup> *i.e.*, any Boolean function can be realized using compositions of functions in this set.

$<sup>^2</sup>$  Phase locking also ensures that the frequency of the oscillator becomes identical to that of the input.

(a) When SHIL happens, the oscillator's frequency locks to the sub-harmonic of the input.

(b) When SHIL happens, phase lock features multi-stability. In this case where  $f_1 \approx 2f_0$ , there are two stable states with 180° phase difference.

Fig. 3. Illustration of frequency and phase lock of sub-harmonic injection locking

The phase response of any amplitude-stable nonlinear oscillator to small external inputs can be captured via a so-called Phase Response Curve (PRC) [22,42,17] or Perturbation Projection Vector (PPV) [7] equation as in (1).

$$\frac{d}{dt}\alpha(t) = \boldsymbol{v}_1^T(t + \alpha(t)) \cdot \boldsymbol{b}(t).$$

(1)

In (1),  $\alpha(t)$  is a changing *time shift* or *jitter* in the oscillator's waveform caused by  $\boldsymbol{b}(t)$ , containing small inputs to the oscillator.  $\alpha(t)$  is related very simply to the phase shift to the oscillator's response.

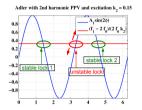

The importance of the PPV equation<sup>3</sup> (1) for oscillator-latches lies in that it can model and predict injection locking effectively [20]; however, though easily solved using numerical methods, analytical solution of (1) is usually not possible. To obtain insights into injection-locking properties, and for visualisation and design, we have developed a simplified approximation of (1) known as the *Generalized Adler Equation* (GAE) [3,2]. Given specific periodic inputs to the oscillator, the GAE governs the dynamics of the oscillator's phase as it evolves; in particular, the equilibrium states of the GAE provide good approximations to injection-locked solutions of the PPV equation (1).

Suppose that the PPV of an oscillator-latch consists of a fundamental sinusoidal component (at the oscillator's natural frequency,  $f_0$ ) of strength  $k_1$ , plus a second harmonic component of strength  $k_2$ . For the oscillator to develop multi stable phase states, we apply a small input SYNC of amplitude  $A_1$  at frequency  $f_1 \simeq 2f_0^4$ . With SHIL, the oscillator changes its frequency to  $f_2 \triangleq \frac{f_1}{2}$  (Fig. 3(a)) and its phase becomes bi-stable (Fig. 3(b)). To control which stable phase the oscillator will latch, we apply another input of amplitude  $A_2$  at frequency  $f_2$ , with phase shift (relative to SYNC)  $\theta^5$ . This input corresponds to one of the stable states thus can be encoded to have a logic value (0 or 1 in binary

<sup>&</sup>lt;sup>3</sup> Well-established computational techniques are available [8,7] to obtain the quantity  $\boldsymbol{v}_1^T(\cdot)$ , known as the PPV or PRC, of any nonlinear oscillator described in differential equations.

<sup>&</sup>lt;sup>4</sup> We have shown that when SYNC is at  $f_1 \simeq m f_0$ , the phase of the oscillator may feature *m* distinct stable states and the analysis performed here is still applicable[3,1]. We will henceforth take m = 2 (binary encoding) to illustrate all the main ideas.

<sup>&</sup>lt;sup>5</sup>  $\theta = 0$  and  $\theta = \pi$  correspond to the two logic states for binary phase logic.

logic). We have shown that the GAE equilibrium equation corresponding to this situation is (2).

$$\frac{f_1 - 2f_0}{2f_0} = k_1 A_2 \sin(\phi - \theta) + k_2 A_1 \sin(2\phi) \,. \tag{2}$$

Solutions  $\phi$  of (2) are the possible phase shifts of the oscillator-latch's waveforms when it is sub-harmonically injection locked. Considerable insight into the number, nature and behaviour of these solutions can be obtained graphically, by plotting its left- and right-hand-sides separately and looking for intersection points.

(a) (2) has 2 stable solutions in the absence of a (logic) input.

(b) Acquisition of input phase: phase bistability of (2) vanishes.

**Fig. 4.** GAE equilibrium equation (2) establishes multi-stability and input phase acquisition properties of oscillator-latches

Fig. 4(a) plots the left- and right-hand-sides (flat red and sinusoidal blue traces, respectively) of (2) when  $A_2 = 0$  and no logic input is present at the oscillator-latch. There are 4 intersections between the two traces, corresponding to 4 solutions of (2). Of these, the first and third intersections (from the left) can be shown to be dynamically unstable<sup>6</sup>; but the second and fourth intersections correspond to two distinct stable oscillations, sub-harmonically locked to SYNC with phases separated by  $\pi$  radians. Thus, in the presence of SYNC, the oscillator-latch features bi-stability.

Fig. 4(b) plots the same left-hand-side (flat red trace), but overlays several traces for the right-hand-side of (2), corresponding to  $A_2$  values 0, 0.035 and 0.1, with the latter two values representing two different strengths of an incoming logical signal at  $f_2$  with  $\theta = 0$ . As can be seen, the first stable intersection remains relatively unaffected as the strength of the incoming input changes, but the second intersection vanishes, structurally, for  $A_2$  value 0.1. This implies that the oscillator acquires the input's logic state. After acquisition, as  $A_2$  is reduced to zero, the GAE can be used to analyze the dynamics of  $\phi$  and show that the acquired logic state is held, even though the second stable intersection is restored.

In summary, the SHIL phenomenon enables the oscillator to develop multiple, well-defined, stable states that can be used to encode logic. It also shows how

<sup>&</sup>lt;sup>6</sup> *i.e.*, they are physically unrealizable in the presence of perturbations, noise or variability.

the oscillator-latch can acquire phase and switch between logic states according to external logic inputs.

#### 3.2 Inherent Noise Immunity of Phase-Based Logic

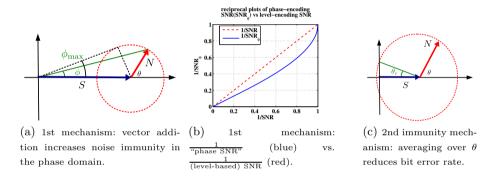

One of the key attractions of encoding logic in the phase of oscillatory signals is that, compared to level-based schemes, phase encoding provides inherent resistance to errors caused by additive noise and interference. There are two aspects to phase encoding that provide intrinsic resistance to additive noise/interference: 1) the effective SNR<sup>7</sup> for phase is increased by a factor of  $\frac{\pi}{2}$  over SNR for levelbased encodings, and 2) the oscillatory nature of the signal whose phase encodes the information makes much of the additive noise/interference average out, leading to smaller bit error rates than for the level-based case. These mechanisms are explained below.

Fig. 5. Mechanisms enhancing the noise resistance of phase-encoded logic

Fig. 5(a) depicts an oscillatory signal as a phasor [12] S, superimposed upon which is a noise (or interference) component, N. The impact of this noise on the phase of the signal is shown by the phase error  $\phi = \angle (S + N)$ . Given fixed amplitudes<sup>8</sup> S = |S| and N = |N|,  $\phi$  depends on the relative angle  $\theta$  between Sand N, *i.e.*,  $\phi = g(\theta, \frac{N}{S})^9$ . For N < S and fixed N/S, there is a maximum phase error over all  $\theta$ , *i.e.*,  $\phi_{\text{max}} = \sin^{-1}(N/S)$ , as depicted in Fig. 5(a). The "phase SNR" is given by  $\text{SNR}_{\phi} = \frac{\frac{\pi}{2}}{\phi_{\text{max}}}$ ; it is the fraction, in angular terms, of the first quadrant taken up by the maximum phase error. This is to be compared against S/N, the SNR for level-based logic (for which, in Fig. 5(a), N is collinear with S). As can be seen from Fig. 5(b),  $\frac{1}{\text{SNR}_{\phi}}$  is always smaller than  $\frac{1}{\text{SNR}}$ , *i.e.*, the "phase SNR" is always improved over the standard level-based SNR. For small S/N (*i.e.*, a large level-based SNR), this improvement is a factor of  $\frac{\pi}{2} \simeq 1.6$ . This is the first mechanism by which phase encoding improves noise immunity.

<sup>8</sup> For illustrative simplicity, we consider noise of only a fixed magnitude. In reality, of course, the magnitude of N has a probability distribution, *e.g.*, a Gaussian one.

<sup>9</sup> For example,  $g(0, \cdot) = g(\pi \cdot) = 0$  and  $g(\frac{pi}{2}, \frac{N}{S}) = \tan^{-1}(\frac{N}{S})$ .

<sup>&</sup>lt;sup>7</sup> Signal to noise ratio.

A second mechanism, conferring additional noise immunity, stems from that the phasors  $\boldsymbol{S}$  and  $\boldsymbol{N}$  are not necessarily always at the same frequency (as assumed implicitly in the analysis of the first mechanism, above), but can rotate at different speeds<sup>10</sup>. Consider now the case where the rotation speeds are very different. The rapid relative change in the angle  $\theta$  between  $\boldsymbol{S}$  and  $\boldsymbol{N}$  suggests that the worst-case phase error  $\phi_{\max}$ , from the first mechanism above, is unduly pessimistic; and that, instead, the phase error *averaged over all values of*  $\theta$  is the appropriate measure. More precisely, the standard deviation  $\sigma_{\phi}$  that results from, *e.g.*, uniformly distributed  $\theta$ , is an appropriate measure of the phase error, This quantity can be substantially smaller than the worst-case phase error  $\phi_{\max}$ , implying considerable additional immunity to noise.

Indeed, this second mechanism makes phase encoding useful even when the noise magnitude is greater than that of the signal, a situation where level-based logic encoding becomes largely useless. This situation is illustrated in Fig. 5(c). Observe that for most values of  $\theta$ , the phase error is less than  $\frac{\pi}{2}$ , the threshold for a bit error. The probability of logical error in the case of phase encoding is  $\frac{\theta_c}{\pi} = \frac{\cos^{-1}(S/N)}{\pi}$ , which can be very small if N is only slightly greater than S (as depicted); and reaches its maximum, 50%, only as the noise increases to infinity. In contrast, the probability of logical error for level-based encoding is always 50% when N > S, since a logical error always results when the noise subtracts from the signal (rather than adding to it).

These noise immunity features of phase encoding do not come as a surprise; the superior noise properties of phase and frequency modulation (PM and FM), over those of amplitude modulation (AM), have long been known [24] and exploited in practice, *e.g.*, in radio communications. However, the authors are not aware of their prior realization, or application, in the context of logic encoding for general-purpose computing.

#### 3.3 Computation with Phase Logic

With phase-based logic encoding, we describe ideas on the implementation of phase-based computing in this section.

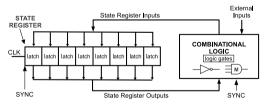

The central unit of a computer is a finite-state machine (FSM) [36]. As is shown in Fig. 6, latches and combinational logic blocks are the key components of an FSM. We first describe how to build combinational logic blocks using phase logic.

We realize combinatorial operations in a manner almost identical to von Neumann's technique,

Fig. 6. A general FSM. SYNC is used to develop multi-stability for encoding phase logic; NOT/MAJORITY gates are for combinatorial operations.

<sup>&</sup>lt;sup>10</sup> The phasor N can be thought of as one component, at frequency f, of a spectral expansion [14] of a stochastic process.

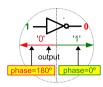

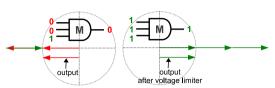

using NOT and MAJORITY operations. Phase logic enables elegant implementation of these two operations: NOT is simply inversion and MAJORITY can be implemented by addition. These can be explained using phasors, as is demonstrated in Fig. 7.

(a) Inverting input signal performs NOT operation in phase logic.

(b) A three-input MAJORITY gate uses addition to perform MAJORITY operation of input signals in phase logic.

Fig. 7. Phase-domain plots illustrating NOT and MAJORITY operations

With oscillator-latches to store phase-based bits and logic gates to perform combinatorial operations, we now have all the components to build generalpurpose computing systems using phase logic. Without loss of generality, here we use CMOS ring oscillators as an example to show how such computing systems can be built.

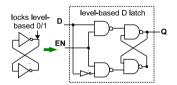

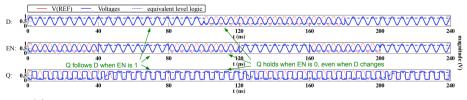

Fig. 8(b) shows a diagram of a D latch implemented using phase logic. The design is analogous to that of a level-based D latch (Fig. 8(a)) except that information is latched in phase. Fig. 8(c) shows waveforms from SPICE-level simulation of the implementation of phase-based D latch with ring oscillators. By aligning the waveforms of Q, D, EN with REF, we see that it achieves the functionality of a transparent D latch in phase logic.

locks phase-based 0/1

(a) Level-based D latch derives from bi-stable level-latching device.

(b) Phase-based D latch derives from bi-stable phasebased bit storage device (*e.g.*CMOS ring oscillator).

(c) Simulation results of phase-based D latch implemented as a CMOS ring oscillator.

Fig. 8. Design and implementation of phase-based D latch

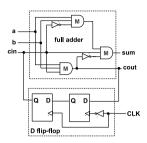

Tying two such transparent D latches together results in an edge-triggered master-slave D flip-flop. With this we build a simplest FSM just to show a flavour of how computation systems operate in phase logic.

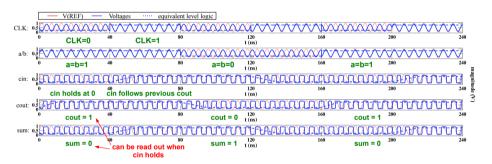

Fig. 9 shows a serial adder made of the D flipflop and a full adder. Just as in the D latch, here we use only MAJORITY and NOT operations in the design for their simplicity of implementation using phase logic. We emphasize again that such a system can be realized using oscillators from various domains. Here we demonstrate its viability using CMOS ring oscillators only as an example and provide simulation results in Fig. 10. We add a = 101 with b = 101 sequentially during three clock cycles. From Fig. 10 we can see *cin* is held stable everytime CLK level is low (translates to having opposite phase as REF). During this time

Fig. 9. Serial adder

cout = 101 and sum = 010 can be read out sequentially. In the full system design their values can then be latched using other registers and connected to following stages in the system, or transformed to level-based logic if connected to other computation or display blocks.

Fig. 10. Waveforms from adding a = b = 101 with serial adder in Fig. 9 implemented using ring oscillator

Even though our scheme is fundamentally different from the conventional computation framework in the way logic is encoded, as we have seen in the examples, the system-level design (FSM design) can be quite analogous to that of level-based logic systems. In this way, all the logic synthesis and timing analysis theories and tools can potentially still be used with only minor modifications, immediately enabling complex, large-scale system design based on phase logic.

#### 3.4 Potential Power/Energy Advantages of PHLOGON

PHLOGON offers significant energy-efficiency benefits over von Neumann's original scheme. It uses continuously-running oscillators, which can be much more energy-efficient than von Neumann's latch-rings. Moreover, neither distribution nor modulation of AC power is involved for running a PHLOGON architecture<sup>11</sup>. This reduces parasitic-related losses especially for large, intricately-routed systems, resulting in significant power savings over von Neumann's scheme.

Compared with level-based CMOS computation architecture, the circuits and nanodevice embodiments of PHLOGON can potentially still be considerably more energy efficient. Dynamic (capacitive charging/discharging) and continuous (sub-threshold leakage) power consumption in level-based CMOS are both strongly determined by the supply voltage. The lowest practical supply voltage today for level-based CMOS is about 0.8V; this number is unlikely to drop significantly in future years, due to threshold voltage, variability and noise barriers [37,38]. In contrast, ring oscillators in standard CMOS technologies operate in sub-threshold mode at supply voltages as low as 80mV [6,10,5]; while in III-V technologies, ring oscillators running at 0.23V were demonstrated almost 30 years ago [11].  $10 \times$  lower supply voltage translates to  $100 \times$  lower dynamic ( $CV^2$ ) power, and more than 20,000 × lower leakage power (exponential in supply voltage). We emphasize that these power savings result simply by moving from level-based to phase-based logic architectures, without any change in the underlying CMOS technology.

Such large power savings can result even with ring oscillators, which dissipate most or all of their energy every cycle. When harmonic oscillators, with Q factors appreciably greater than 1, are used, further energy savings<sup>12</sup> can be realized. On-chip CMOS LC oscillators with spiral inductors, though considerably larger in area than ring oscillators, are available today with Q factors greater than 10, making them an interesting candidate to explore for additional power efficiency. Integrated MEMS resonators, though even larger in area, feature Q factors of  $10^4$ - $10^5$  [26], potentially making them extremely attractive for low power computation with easily available and well-developed conventional technologies. Resonant Body Transistor (RBT), a silicon-based resonator compatible with standard CMOS process, has been demonstrated to achieve >10GHz frequency with Q factor of 1830 [40], making it another promising candidate. Spin-torque nano-oscillators (STNOs) feature Q factors of more than  $10^4$  at frequencies of 25GHz [31,18,32]; as such, they offer very exciting power, as well as speed, possibilities.

### 4 Conclusions

In this paper we re-examined Goto and von Neumann's phase-based logic ideas and limitations of their previous implementations. We proposed enhancements to them, showing that almost any DC-powered, self-sustaining nonlinear oscillator can be used to build latches and combinatorial elements, enabling phasebased computing. We provided mathematical tools for analysing SHIL as the

<sup>&</sup>lt;sup>11</sup> Note that SYNC and CLK can be weak, dissipating negligible power.

$<sup>^{12}\,</sup>$  *i.e.*, an energy advantage of roughly Q over ring oscillators using the same technology and supply voltage.

mechanism for phase-based logic encoding. We showed that phase logic offers inherent resistance to noise and variability and also discussed the potential energyefficiency our scheme may achieve. These features have made PHLOGON an interesting and promising alternative to the conventional level-based computation architecture. We are currently exploring design details and tradeoffs involved in the practical manifestation of PHLOGON in post-CMOS and standard digital CMOS technologies.

Acknowledgements. The authors would like to thank Rajiv Mathur, FCRP liaison in Intel, for pointing us to von Neumann's original works. We would also like to thank the reviewers for the useful comments and in particular anonymous reviewer No.2 for pointing us to Goto's patent on resonator circuits.

# References

- Neogy, A., Roychowdhury, J.: Analysis and Design of Sub-harmonically Injection Locked Oscillators. In: Proc. IEEE DATE (March 2012)

- [2] Adler, R.: A study of locking phenomena in oscillators. Proceedings of the I.R.E. and Waves and Electrons 34, 351–357 (1946)

- Bhansali, P., Roychowdhury, J.: Gen-Adler: The generalized Adler's equation for injection locking analysis in oscillators. In: Proc. IEEE ASP-DAC, pp. 522–227 (January 2009)

- [4] Buck, J., Buck, E.: Synchronous fireflies. Scientific American (1976)

- [5] Cilek, F., Seemann, K., Brenk, D., Essel, J., Heidrich, J., Weigel, R., Holweg, G.: Ultra low power oscillator for UHF RFID transponder. In: Proc. IEEE Freq. Contr. Symp., pp. 418–421 (May 2008)

- [6] Deen, M.J., Kazemeini, M.H., Naseh, S.: Performance characteristics of an ultralow power VCO. In: Proc. IEEE ISCAS (May 2003)

- [7] Demir, A., Mehrotra, A., Roychowdhury, J.: Phase Noise in Oscillators: a Unifying Theory and Numerical Methods for Characterization. IEEE Trans. Ckts. Syst. – I: Fund. Th. Appl. 47, 655–674 (2000)

- [8] Demir, A., Roychowdhury, J.: A Reliable and Efficient Procedure for Oscillator PPV Computation, with Phase Noise Macromodelling Applications. IEEE Trans. on Computer-Aided Design, 188–197 (2003)

- [9] Eiichi, G.: Resonator circuits, US Patent 2,948,818 (August 9, 1960)

- [10] Farzeen, S., Ren, G., Chen, C.: An ultra-low power ring oscillator for passive UHF RFID transponders. In: Proc. IEEE MWSCAS, pp. 558–561 (August 2010)

- [11] Feuer, M.D., Hendel, R.H., Kiehl, R.A., Hwang, J.C.M., Keramidas, V.G., Allyn, C.L., Dingle, R.: High-speed low-voltage ring oscillators based on selectively doped heterojunction transistors. IEEE Electron Device Letters EDL-4, 306–307 (1983)

- [12] Giancoli, D.C.: Physics for Scientists and Engineers. Prentice-Hall, Englewood Cliff (1989)

- [13] Goto, E.: New Parametron circuit element using nonlinear reactance, KDD Kenyku Shiryo (1954)

- [14] Grigoriu, M.: Stochastic Calculus: Applications in Science and Engineering. Birkhäuser, Boston (2002)

- [15] Hoe, W., Goto, E.: Quantum Flux Parametron: A Single Quantum Flux Superconducting Logic Device. Studies in Josephson Supercomputers, vol. 2. World Scientific (1991)

- [16] Huygens, C.: Horologium Oscillatorium. Apud F. Muget, Paris (1672); Observations of injection locking between grandfather clocks

- [17] Izhikevich, E.M.: Dynamical Systems in Neuroscience: The Geometry of Excitability and Bursting (Computational Neuroscience), 1st edn. The MIT Press (November 2006)

- [18] Kaka, S., Pufall, M.R., Rippard, W.H., Silva, T.J., Russek, S.E., Katine, J.A.: Mutual phase-locking of microwave spin torque nano-oscillators. Nature 437, 389–392 (2005)

- [19] Kurokawa, K.: Injection locking of microwave solid-state oscillators. Proceedings of the IEEE 61, 1336–1410, 1386–1410 (1973)

- [20] Lai, X., Roychowdhury, J.: Capturing injection locking via nonlinear phase domain macromodels. IEEE Trans. Microwave Theory Tech. 52, 2251–2261 (2004)

- [21] Mahboob, I., Yamaguchi, H.: Bit storage and bit flip operations in an electromechanical oscillator. Nature Nanotechnology 3, 275–279 (2008)

- [22] Malkin, I.G.: Some Problems in Nonlinear Oscillation Theory, Gostexizdat, Moscow (1956)

- [23] Manley, J.M., Rowe, R.E.: Some general properties of nonlinear elements Part I. General energy relations. Proceedings of the Institute of Radio Engineers 44, 904–913 (1956)

- [24] Middleton, D.: An Introduction to Statistical Communication Theory. Wiley-IEEE, New York (1996)

- [25] Muroga, S.: Elementary principle of Parametron and its application to digital computers. Datamation 4, 31–34 (1958)

- [26] Nguyen, C.T.-C.: Vibrating RF MEMS for Next Generation Wireless Applications. In: Proc. IEEE CICC (May 2004)

- [27] Oshima, Enemoto, Watanabe: Oscillation theory of Parametron and method of measuring nonlinear elements, KDD Kenkyu Shiryo (1955)

- [28] Oshima, S.: Introduction to Parametron. Denshi Kogyo 4, 4 (1955)

- [29] Bhansali, P., Srivastava, S., Lai, X., Roychowdhury, J.: Comprehensive Procedure for Fast and Accurate Coupled Oscillator Network Simulation. In: Proc. ICCAD, pp. 815–820 (November 2008)

- [30] Kinget, P., Melville, R., Long, D., Gopinathan, V.: An injection-locking scheme for precision quadrature generation. IEEE J. Solid-State Ckts. 37, 845–851 (2002)

- [31] Pufall, M.R., Rippard, W.H., Kaka, S., Silva, T.J., Russek, S.E.: Frequency modulation of spin-transfer oscillators. Applied Physics Letters 86, 82506 (2005)

- [32] Rippard, W.H., Pufall, M.R., Kaka, S., Silva, T.J., Russek, S.E., Katine, J.A.: Injection locking and phase control of spin transfer nano-oscillators. Phys. Rev. Lett. 95, 067203 (2005)

- [33] Strogatz, S.: Sync: The Emerging Science of Spontaneous Order, Theia (March 2003)

- [34] Strogatz, S.H., Stewart, I.: Coupled oscillators and biological synchronization. Scientific American 269, 102–109 (1993)

- [35] Takahashi, H.: The Parametron. Tsugakkat Shi 39, 56 (1956)

- [36] Taub, A.H. (ed.): John von Neumann: Collected Works. Design of Computers, Theory of Automata and Numerical Analysis, vol. V. Pergamon Press, New York (1963)

- [37] Toh, S., Tsukamoto, Y., Guo, Z., Jones, L., Liu, T., Nikolic, B.: Impact of random telegraph signals on Vmin in 45nm SRAM. In: Proceedings of the IEEE International Electron Devices Meeting, pp. 767–770 (2009)

- [38] Tsukamoto, Y., Toh, S., Shin, C., Mairena, A., Liu, T., Nikolic, B.: Analysis of the relationship between random telegraph signal and negative bias temperature instability. In: Proceedings of the IEEE International Reliability Physics Symposium, pp. 1117–1121 (2010)

- [39] von Neumann, J.: Non-linear capacitance or inductance switching, amplifying and memory devices (1954)

- [40] Weinstein, D., Bhave, S.A.: The resonant body transistor. Nano Letters 10, 1234–1237 (2010)

- [41] Wigington, R.L.: A New Concept in Computing. Proceedings of the Institute of Radio Engineers 47, 516–523 (1959)

- [42] Winfree, A.: Biological Rhythms and the Behavior of Populations of Coupled Oscillators. Theoretical Biology 16, 15–42 (1967)